电机芯片应用硬件设计指导

# 硬件设计

# 主控MCU选型

### 技术特点:

- JS32M041内置低压预驱模块可以直接驱动3路(P+N)MOS,内置LDO可以为外围提供5V/30mA电源

- 支持有感无感FOC、方波、SVPWM 控制

- 内部集成2路运放和2路比较器

- 内置硬件乘法器和硬件除法器,提高运算速率

- 支持单/双电阻电流采样

#### 应用场景:

- 生活电器: 高速吹风筒、落地扇、高压风扇、油烟机、空气净化器等;

- 电动工具: 水泵、鼓风机等;

- 其他:减速电机、离心机等。

# 选型表

| 型号        | 封装     | 内置LD0 | 内置预驱             |    | PWM            | UART | ADC | COMP | OPAM |

|-----------|--------|-------|------------------|----|----------------|------|-----|------|------|

| JS32M040E | SSOP24 | 无     | 无                | 22 | 3 互补+<br>15 独立 | 2    | 7   | 2    | 2    |

| JS32M040G | LQFP32 | 无     | 无                | 27 | 3 互补+<br>15 独立 | 2    | 13  | 2    | 2    |

| JS32M040L | LQFP48 | 无     | 无                | 42 | 3 互补+<br>15 独立 | 2    | 13  | 2    | 2    |

| JS32M041E | SSOP24 | 有     | 3路P+N<br>(6-36V) | 13 | 3 互补+<br>15 独立 | 2    | 7   | 2    | 2    |

| JS32M041L | LQFP48 | 有     | 3路P+N<br>(6-36V) | 35 | 3 互补+<br>15 独立 | 2    | 13  | 2    | 2    |

# 原理图设计

# 功能模块设计

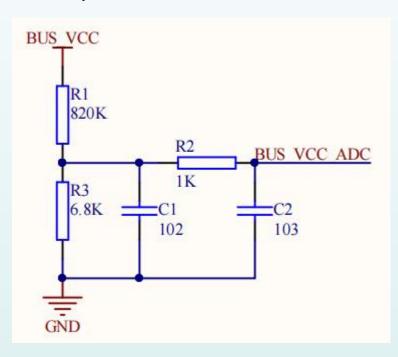

#### a) 母线电压采样电路设计

在FOC的SVPWM模块中需采集母线电压进行计算,而在无刷电机应用中,因电源电压与MCU的ADC最大采样电压相差很大,要根据实际情况将母线电压用电阻分压的方式来进行处理,才能给到MCU。采样电路中的分压电阻R1,R3,采样电压比值计算 $R_V$ =R3/(R1+R3),母线最大采样电压为Vsmax= $V_S$ / $R_V$   $V_S$ 表示MCU的ADC最大采样电压。

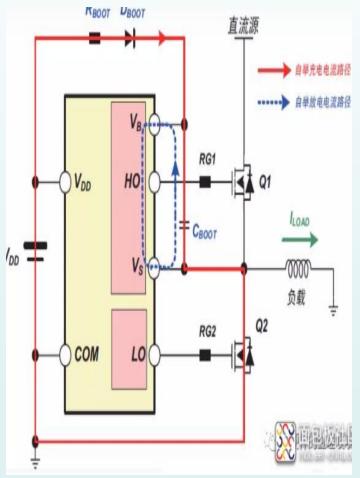

#### b) 自举电路设计

Q1,Q2作为上下管工作时只能有一个管子导通。 $V_s$ 连接负载,电压是浮动的,当下管导通时, $V_s$ 被拉到GND,也可认为负压 $V_n$ ; 当上管导通时, $V_s$ 被拉到直流源主电压。驱动MOS管完全导通的电压在15V左右,即MOS管的 $G_s$ 之间要保持15V左右的稳定压差。既然VS端是浮动的,那么Q1的栅极电压也应该叠加在 $V_s$ 上随着 $V_s$ 的变化而变化,让 $V_{GS}$ 的压差始终稳定,这样才能正常驱动上MOS管。如何保持这个压差,那就需要靠自举电容 $C_{boot}$ 和自举二极管 $D_{boot}$ 。

当下管Q2导通,自举电容通过自举二极管,被供电电压 VDD瞬间充电。

当驱动上管Q1导通时,自举电容通过其给外部上管驱动 $G_S$ 供电,关断时内部下MOS导通,使得驱动外部的MOS管 $G_S$ 寄生电容有放电的路径,从而达到快速关断的目的。(电阻 $R_{boot}$ 作用是充电周期内限流,二极管 $D_{boot}$ 作用是在上管完全导通的时候,防止电容通过供电回路放电。)

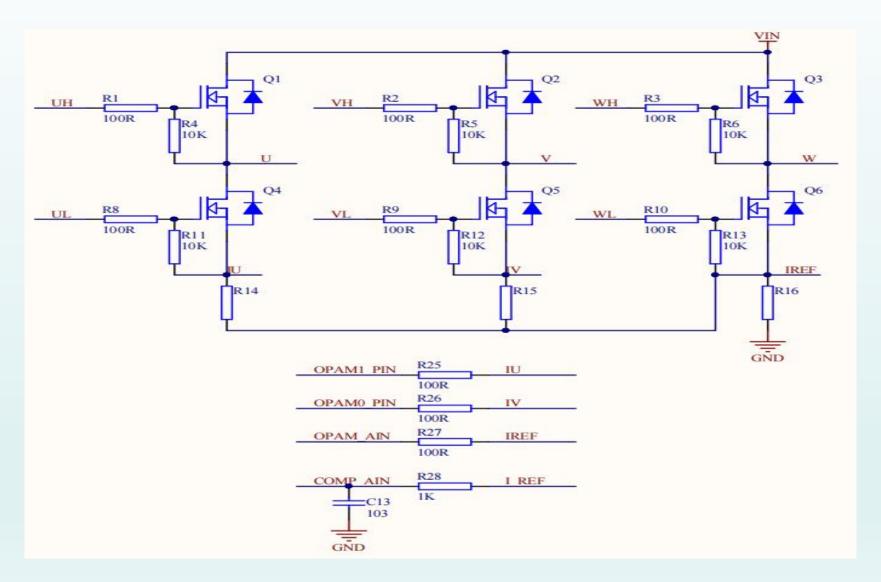

#### c) 相电流采样电路设计

在实际应用中,采样电阻越大越好,放大倍数越小越好。采样电阻很小,运算放大倍数很大,这样干扰也会跟着放大,导致采样数据不准确。采样电阻阻值变大2倍,相同电流的情况下,功率也变大2倍,同时功耗也会变大2倍,价格也相应的增加很多。所以采样电阻选择要综合考虑成本和性能取一个合适的值。通常我们是按照理论上的最大电流来计算一个合适的阻值,阻值一般情况下要低于0.5Ω、精度为1%的常规物料,封装要在1206、1210、2110、2512等中选择。放大倍数一般为3-10倍。

例如下图客户要求电机功率为60W,额定工作电压为24V,最低工作电压为20V,通过电机参数计算,最大额定电流60/20=3A,最大电流3\*1.414=4.242A,采样电阻采用0.03Ω,采样电阻最大功率为0.54W,考虑到温升影响至少要降额使用70%,所以最好选择1W或者以上功率的采样电阻,综合价格等因素,这里选择0.03Ω/1W的采样电阻。在采样电阻基本确定的情况下,放大倍数一定要留有足够的余量,通常的余量为最大电流的2倍以上,这里的最大电流为4.242A,按照5A计算,一般情况下,我们要选择可以采样两倍最大电流的范围。可采样范围为2.25±2.25V,2.25/0.03/10=7.5倍,这里选择8倍,所以可采样电流范围为10A,满足设计要求。

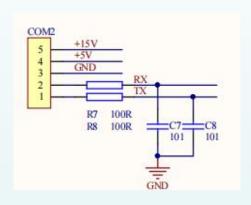

#### d) UART电路设计

当用到UART通信时,应在通讯信号线TX、RX上加RC滤波网络,以提高UART的抗扰性,RC参数选择电阻100R、电容值100pF。

#### e) SWD接口电路设计

SWD 口支持复用功能,当 PA13/PA14 复用为其他功能时,此 IO 口上禁止并 100pF 以上大电容,否则会造成 SWD 功能无法正常使用。SWD-CLK 管脚禁止用作输入模式,防止 SWD-CLK 管脚电平不确定导致无法正常上电。

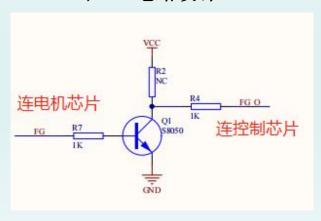

#### f) FG电路设计

FG: 转速反馈输出端口,信号输出为集电极开路输出型。当FG线受到干扰时,要加RC滤波电路。

## 注意事项

- a) 使用高级控制定时器(TIMER1)产生PWM信号驱动电机时,可以用TIM2或TIM3 定时器作为"接口定时器"来连接霍尔传感器,3个定时器输入脚CH1、CH2、CH3。

- b) JS32M041系列芯片内置预驱和LDO。VIN脚建议输入电压控制在6-24V之间,输入电压超过24V时LDO压降大造成芯片发烫厉害。AVCC引脚可以为外部负载提供50mA/5V电源。

- c) JS32M041系列芯片AVCC引脚给外部负载供电需要在AVCC和AVSS引脚间并 1uF-10uF和0.1uF贴片瓷片电容。

- d) S32M041系列芯片VIN脚与AVSS引脚间并10uF和0.1uF贴片瓷片电容。

- e) 所有连接线路板接插件的IO口都要串联1K以上的电阻,防止芯片被外部ESD或EOS损坏。

- f) 当使用芯片IO口做捕获PWM功能时,请不要选择带N的定时器。

- g) JS32M040系列芯片要在芯片的VCC对VSS、AVCC对AVSS引脚间并1uF和0.1uF贴片电容。

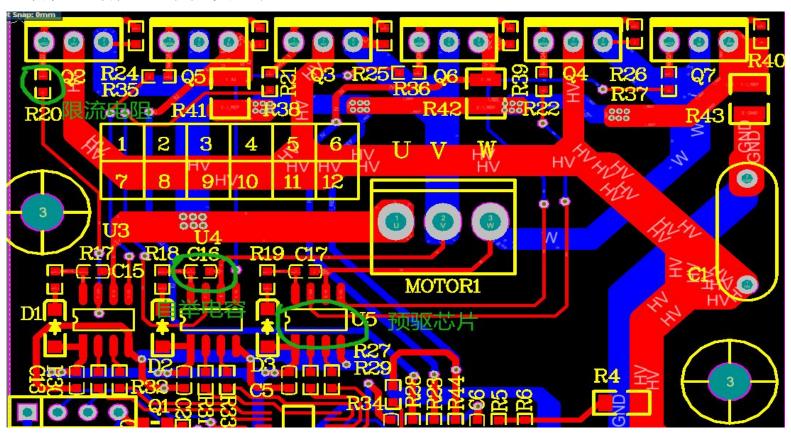

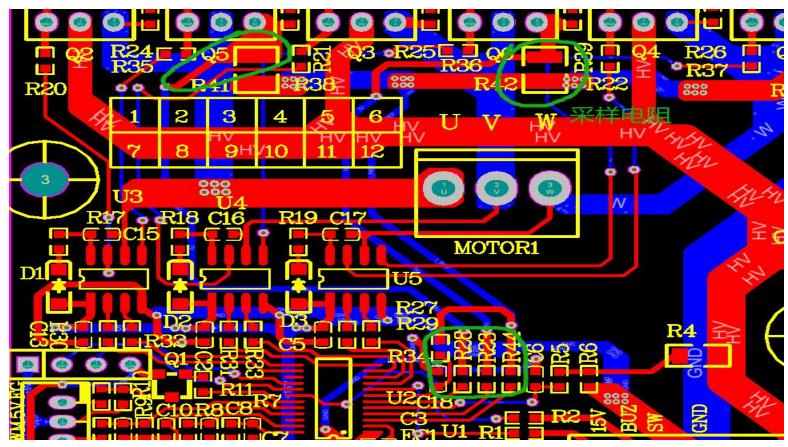

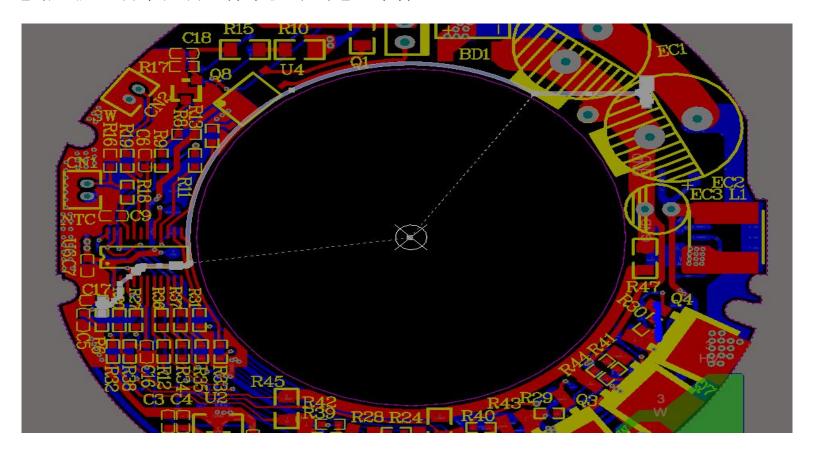

# PCB Layout设计

### PCB布局规范

- a) 优先放置与结构有紧密相关的元器件,如电源插座、指示灯、按键、连接器等。再放置特殊元器件,如大的元器件、重的元器件、发热元器件、变压器、IC等。最后放置小的元器件。

- b) 按照电路图的各功能电路单元布局,使信号尽可能保持一致的方向。 以每个功能单元的核心元器件为中心,围绕它来进行布局。元器件应均匀、 整齐、紧凑的排列在PCB上,尽量缩短各元器件之间的走线。这样不但美 观,而且装焊方便,便于批量生产。

- c) 易受干扰的电路单元模块的布局要远离开关单元模块和发热单元模块

- d) 整体布局时,发热器件周围要预留足够的空间,方便散热。

- e) 强电电路模块和弱电电路模块要分开布局,防止互相干扰。

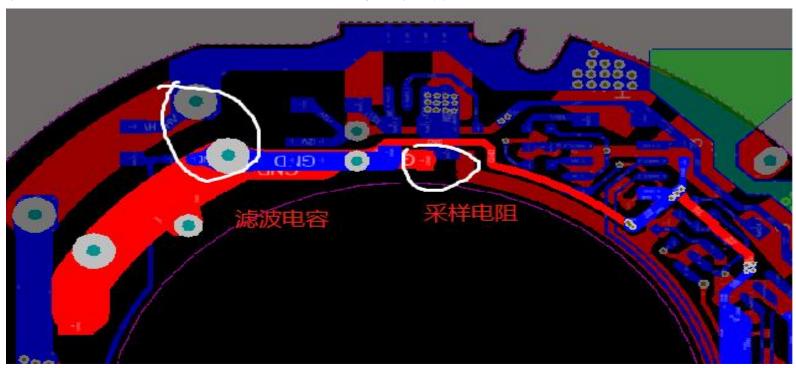

- f) 采样电阻一定要靠近功率控制器件(MOS/IGBT)放置。

- g) 运放和比较器的配置电容、电阻要靠近MCU引脚放置。

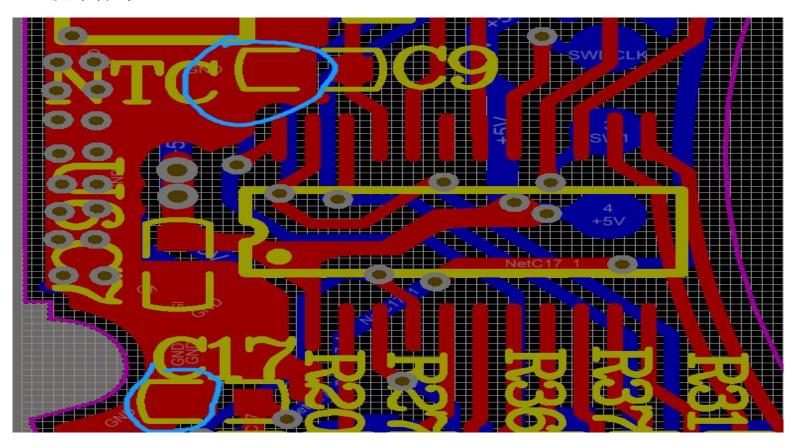

- h) 母线电压采样模块一定要远离功率控制器件(MOS/IGBT)电路,防止功率控制器件电路对母线电压采样干扰。

- i) MCU电源引脚的滤波旁路电容一定要靠近芯片放置。

## PCB走线规范

a) 电源和地走线规范:回路越短干扰就越小,通常采用双回路原则。整个线路板的大功率器件走线回路要最短,同时要包围的面积最小,最好是靠近线路板的一边放置,尽量做到不对其他电路产生干扰。采样电阻的地和其他电路的地分两组走线,采用单点接地的方式连接到滤波电容的负端引脚处。

b) 驱动部分电路模块走线规范:良好的驱动走线,是驱动控制部分稳定的基础,控制部分稳定才能保证采样的稳定。如果驱动控制部分有问题,采样再精准,也会失真。预驱芯片到功率器件(MOS/IGBT)的驱动信号,通常将驱动IC靠近功率器件放置(MOS/IGBT),驱动IC发出的信号通过限流电阻等连接到功率器件,此处的走线要尽量简单、不要交叉且限流电阻最好是靠近功率器件放置。自举电容要靠近预驱芯片放置,走线尽量短。

c) 采样信号线走线规范:采样电阻到功率器件(MOS/IGBT)走线一定要断而粗,因为采样电阻的阻值都是毫欧级的,当走线比较细时,走线阻抗对采样值影响比较大。采样信号线尽量不要有过孔,如果受布局和空间受限必须加过孔,建议从本层引出一段距离后,远离采样电阻后再打过孔。

d) 母线电压采样走线规范:母线电压采样走线要避开功率控制器件(MOS/IGBT)电路,防止功率控制器件干扰母线电压采样。

e) 其他信号线走线规范:当信号线加了RC滤波电路时,RC电路的电容的地一定要和MCU的地连接在一起走线。精密信号的采样,尤其是和ADC相关的信号,相关器件的GND一定要与MCU的GND直接相连,如电流采样,电压采样,温度采样等。